基于FPGA的基带64×64数据分配矩阵设计方案

本文采用FPGA作为实现控制逻辑的核心部件,提出了基于FPGA的基带64×64 数据分配矩阵设计方案,并介绍了上位机的软件设计思路和FPGA的内部编程实现及仿真。经验证该方案具有规模大、成本低、高速等特点,可广泛应用于大规模基带数字系统测试及信号程控分配调度中。

本文引用地址://www.cghlg.com/article/221565.htm0 引言

数据分配矩阵即矩阵开关,顾名思义,指结构为行列交叉排布的开关产品,其特点为每个节点连接一个行 /列,每个节点可以单独操作,通过设置节点的不同组合可以实现信号的路由。矩阵开关的主要优势在于其简化的部线,整个测试系统可轻松地动态改变其内部连接路径而无须外部手动干预。矩阵开关的使用非常灵活方便,是目前程控开关产品中品种最多的产品,在汽车电子、半导体测试、航空航天等领域得到了广泛的应用。

FPGA具有运行速度快,内部逻辑资源丰富,外围I/O口数量多等优点,因此本设计选用FPGA作为核心器件。

1 系统结构及功能

本设计是为了实现64位输入信号到64位输出的任意无交叉的切换,即输入与输出是一一对应的。由于本设计是针对基带数字信号,而设计中选用的晶振频率为25 MHz,因此根本不用考虑FPGA处理异步时钟域数据传输的问题,只需直接将对应的输入信号经电平转换后,经译码后直接输出到相应的某路输出接口即可。

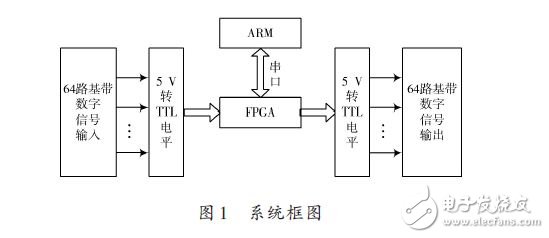

上位机ARM 通过串口向FPGA 发送接口的连接信息,FPGA根据接收到的数据进行译码,将对应的输入与对应的输出连接起来,实现规定链路的连接。考虑到所含资源以及管脚数量,本设计方案选用Altera公司Cyclone Ⅲ系列EP3C25F256型FPGA.选用了4块32路的电平转换芯片实现5 V 信号向FPGA 能够识别的TTL 信号的转换。

其结构框图如图1所示。

2 上位机设计

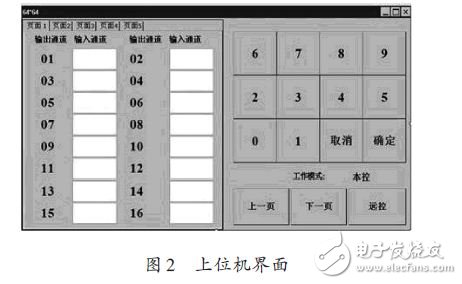

上位机的界面如图2 所示。在相应的输入通道文本框里输入0~64,点击“确定”按钮后,首先对文本框里所有的数据进行比较判断,如出现重复则进行报错,提示重新输入。无误后,通过串口按输出接口顺序依次向FPGA发送64条接口的连接指令。每一条指令包含3 B,第一个字节为信息头“AA”,若FPGA接收到的某条指令的头字节不是“AA”,则无返回信息,上位机将重新发送这条指令直到正确为止。第二个字节为输入端口字节,即对应文本框中的数字,如没有输入数字则默认发送0,所以如需端口某条链路断开只要在相应的文本框中输入0,点击确定即可。第三个字节为输出端口对应的数据,按1到64顺序发送。图2中的“远控”按钮为预留的用作计算机远控使用。

3 下位机设计

3.1 串口通信协议

串行通信是一种可以将接收到的并行数据字符转换为连续的串行数据流发送出去,同时可将接收的串行数据流转换为并行的数据字符发送出去的通信协议。

其数据帧主要包括1位起始位,8位数据位,1位奇偶校验位,1/2位停止位。

3.2 FPGA内部编程

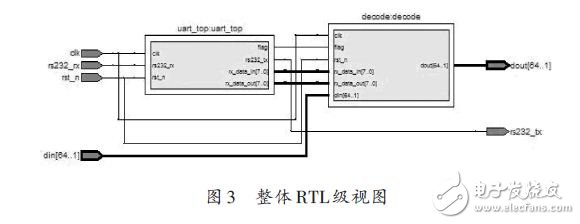

FPGA模块的主要功能是实现串口收发和译码,相应地在用Verilog HDL实现时也分为串口收发和译码2个电路模块,经综合后其RTL级视图如图3所示。开发工具采用Altera公司推出的集成EDA 开发工具Quartus Ⅱ,可以完成Altera公司所有的FPGA /CPLD产品开发的设计输入、综合、实现等环节。

fpga相关文章:fpga是什么

晶振相关文章:晶振原理

评论