System Generator是一个功能强大的工具,它将Xilinx FPGA设计过程与MATLAB的Simulink集成,后者使用高级描述轻松实现复杂系统。我们首先设计系统并在Simulink环境中验证其功能。Simulink的图形化高级描述极大地简化了设计的建模,仿真和分析。然后,我们可以生成设计的VHDL描述,并将其添加到Xilinx ISE软件中的项目中。

在本文中,我们将讨论使用Xilinx System Generator实现简单的直接数字频率合成器(DDS)。

启动System Generator

在启动System Generator之前,您应该注意两点:

确保您的System Generator版本与您将要使用的MATLAB版本兼容。

将MATLAB软件与System Generator关联。

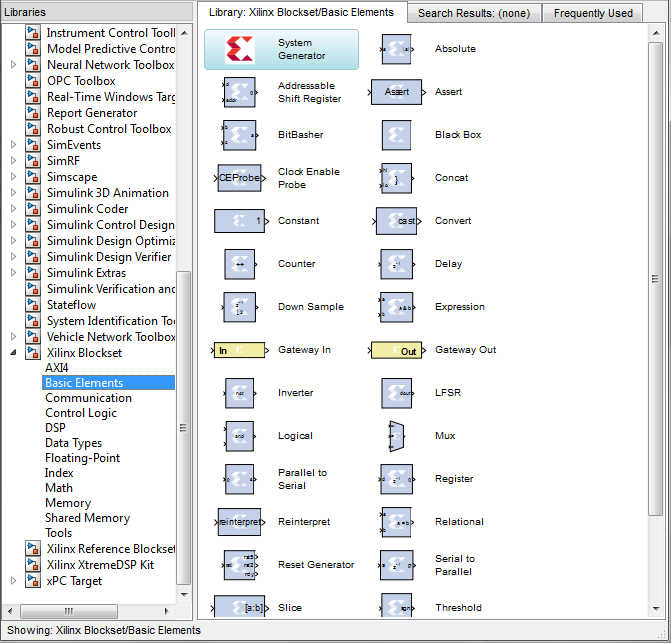

在本文中,我将使用ISE 14.7和MATLAB 2013a。启动System Generator的推荐方法是从Windows的“所有程序”菜单中选择“Xilinx设计工具\ ISE设计套件14.7 \系统生成器\ Sysgen生成器”。这将打开“Simulink Library Browser”,如图1所示。

如图所示,以下三个Xilinx类别被添加到库列表中:

Xilinx模块组

Xilinx参考模块组

Xilinx XtremeDSP套件

在本文中,我们将使用“Xilinx Blockset”中提供的块来实现简单的DDS,如图2所示。

为DDS创建系统生成器模型

要创建新的Simulink模型,请选择File \ New \ Model。这将打开以下空白窗口,允许我们描述图2的框图。

在本文的其余部分,我们将添加所需的构建块并查看每个块的对话框中的重要设置。有关不同块的可配置参数的更多信息,请参阅此Xilinx文档。

AddSub Block

我们需要的第一个块是加法器。我们可以使用“AddSub”块,可以在“Xilinx Blockset \ math”类别中找到。下面的图4显示了该块的可配置参数的符号和“基本”选项卡。

该块有两个输入(a和b)和一个输出,给出+ b。我们将保留“基本”选项卡的参数。“输出”选项卡的设置如图5所示。此选项卡设置输出的参数。要有一个16位累加器,我们选择“用户定义”选项,它允许我们将“位数”设置为16,将“二进制点”设置为零。这意味着输出是16位整数。对于图2的DDS,我们不需要定义分数输出,但是,如果我们将“位数”设置为16并将“二进制点”设置为14,则总共16位中的14位输出将被视为二进制点的右侧。

“算术类型”和“溢出”是另外两个对我们很重要的参数。“算术类型”应该是无符号的,因为累加器的输出被解释为无符号数。“溢出”应设置为“自动换行”,因为累加器应在达到最大值时翻转。

图6显示了块的“Implementation”选项卡。在此页面中,您可以选择使用Fabric或DSP48切片实现加法器。有关两种选择之间差异的讨论。我们将默认保留它,即使用Fabric实现。

接下来,我们将在加法器的输出处添加寄存器集。可以使用“Xilinx Blockset \ Basic Elements”类别中的“Delay”块实现寄存器。我们将保留此块的所有设置。

将“AddSub”块连接到“Delay”块,我们得到如图7所示的原理图。

量化

现在,我们需要添加图2的“量化器”,它将累加器的p个最高有效位(MSB)传递给查找表(LUT)并丢弃其他位。使用“Xilinx Blockset \ Basic Elements”类别中的“Slice”块可以实现此功能。“切片”的符号和可配置参数对话框如图8所示。

参数“切片宽度(位数)”指定从输入中提取的位数。假设累加器输出的8个MSB必须传送到LUT,我们知道输出的宽度是8,所以我们将“切片宽度”设置为8,如图所示。

我们还需要指定输入的哪些位位置来形成“Slice”块的8位输出。这可以使用“指定范围为”参数来完成。此参数有三个选项。我们选择“高位位置+宽度”。我们应该从输入中指定高位的位置,该输入将被传递到“Slice”输出的MSB。由于我们需要输入的8个MSB,因此高位将是输入的MSB。因此,我们将“顶部位偏移”设置为零,将“相对于”设置为“输入的MSB”。这意味着上部所需位相对于输入的MSB具有零偏移。切片的宽度已在“切片宽度”参数中指定。因此,完全指定了所需的输入范围。

只读存储器

28=256可以在“输出”选项卡下选择存储值的数据格式。我们将使用默认参数,如图10所示。注意“算术类型”是“有符号(2的comp)”,因为我们的样本包含负值。从输出的总共16位仅将两位分配给整数部分,因为样本的最大值和最小值分别为+1和-1。其余位用于表示样本的小数值。

Xilinx部分与Simulink之间的数据类型转换

根据图2连接讨论的块,我们得到如图11所示的原理图。

模型几乎完成,但我们需要一些其他模块来模拟系统。与使用定点数表示不同值的Xilinx模块组不同; Simulink环境有自己的数据类型。例如,Simulink可以使用“双”数据类型,它是64位二进制补码浮点数。这就是为什么在将数据从Simulink传输到图11的Xilinx部分或将图11的输出传输到Simulink环境时,我们需要一些块来执行数据类型转换。这可以使用“Gateway In”和“Gateway Out”块来实现,如图12所示ICfans。

我们将在一分钟内查看“Gateway In”和“Gateway Out”块的参数,但在此之前,您应该注意另外两个块,输入处的“Step”和输出处的“Scope”,添加到模型中。如您所见,在添加“Gateway In”和“Gateway Out”块之后,我们可以使用Simulink通用“Source”块将输入应用于我们的模型。或者,我们可以通过Simulink通用“Sink”块监视系统的输出。在图12中,我们对DDS的相位增量输入应用了“步”。此外,使用Simulink“Scope”块监视ROM的输出。

除数据类型转换外,“Gateway In”和“Gateway Out”块定义HDL设计的顶级端口,稍后将从Simulink模型中获取。例如,在加法器的“a”输入之前放置一个“Gateway In”块,我们让系统生成器知道“a”输入实际上是顶层设计的输入。同样,“网关输出”定义了HDL设计的顶级输出。

“Gateway In”块的可配置参数对话框如图13所示。

我们应该将“算术类型”设置为“无符号”并选择“比特数”等于16而没有小数位,即“二进制点”= 0。因此,来自Simulink环境的任何输入都将在设计的Xilinx部分中表示为16位定点无符号数。请注意,我们在此处指定的格式与Add / Sub块的数据格式一致。默认情况下,我们将保留块的其他参数。

“网关输出”块自动检测其驱动阶段的定点格式。这就是为什么我们可以使用块的默认设置。

Xilinx系统发生器模块

任何使用Xilinx模块的Simulink模型都必须包含“System Generator”模块。该块允许我们控制系统和模拟参数。它还处理HDL代码生成。“System Generator”块的符号和对话框如图14所示。

System Generator将设计编译为低级表示。我们可以从对话框的“编译”参数中选择低级表示的类型。在本文中,我们将选择“HDL Netlist”,如图所示。这将生成一组HDL和一些可由综合工具处理的辅助文件。如图所示,我们分别选择了“XST”和“VHDL”作为综合工具和HDL。

您还应该从对话框的“部件”参数中选择目标设备,并为软件提供目标文件夹以存储生成的文件。下面的图15显示了对话框的“Clocking”选项卡。

第一个参数“FPGA时钟周期(ns)”定义了设计所需时钟的周期。该参数可以在设计的下一阶段传递给综合工具。它可以指导综合软件根据设计的时钟要求选择合适的实现方案。在上图中,“FPGA时钟周期”设置为10纳秒。这意味着我们希望设计在电路板上以10ns的时钟周期运行。Simulink可以在其模拟中使用此时钟周期的标准化形式。此标准化由图15的“Simulink系统周期(秒)”参数指定。通过将此参数设置为1,在Simulink环境中,每10 ns的硬件实现将表示1秒。

模拟

为了模拟设计,我们将“Step”输入设置为在“Step time”500处从264到528.您可以使用该块的其他任意参数。最后,我们准备模拟我们的DDS模型,如图16所示。

通过单击Simulink的“运行”按钮,我们在“范围”上得到以下曲线。

由于在“步进时间”= 500时,输入从264变为528,输出频率增加了两倍。

将设计添加到ISE项目

在设置了设计的所有参数之后,我们可以通过按下图14中的“Generate”按钮来生成模型的VHDL描述。这将生成一个“.sgp”文件,可以将其添加到ISE项目中。

通过从ISE项目中选择“添加源”,我们可以在顶级设计中包含.sgp文件。现在,添加的文件可以像我们使用IP核一样使用。通过单击添加的文件并选择“查看HDL实例化模板”,我们可以找到使用该组件的模板。

结论

在本文中,我们使用“System Generator”来实现一个简单的DDS。Simulink的高级图形功能使我们能够轻松地为复杂的数字系统建模。在Simulink环境中验证设计的功能后,我们可以生成设计的VHDL描述并将其添加到Xilinx ISE软件中的项目中。