又一芯片巨头宣布背面供电技术突破

半导体技术的许多进步都取决于减小封装尺寸,同时结合附加功能和更高效的供电方法。目前的供电方法会占用晶圆上的大量空间,导致成本增加、芯片尺寸增大和晶体管减少。今年早些时候,三星半导体展示了其关于传统半导体供电方法的替代方案的研究:背面供电。这可能导致芯片尺寸的显著减小和布线拥塞的减少。

本文引用地址://www.cghlg.com/article/202308/449609.htm根据 TheElec 和三星在今年超大规模集成(VLSI)研讨会上的演讲报告,与传统的前端供电网络(PDN)相比,新的背面供电网络(BSPDN)方法成功地将所需的晶圆面积减少了 14.8%。成功实施后,两个 ARM 电路的面积分别减少了 10.6% 和 19%,同时布线长度减少了 9.2%。

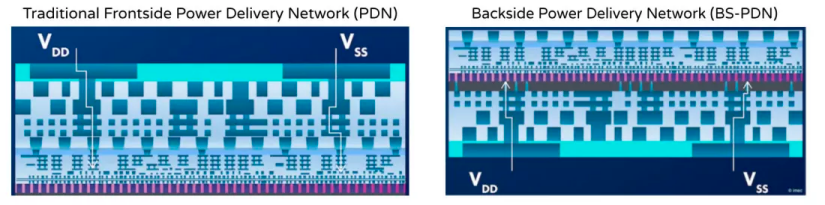

在传统的前端 PDN(FSPDN)中,半导体元件必须布置在晶圆的正面,以便提供从电源线到信号线和晶体管的传输。这种配置需要在传输和信号网络之间共享空间和资源,越来越抗的路由以在线路后端堆栈上传输电子,并且可能导致在传输到半导体结构中的接地轨期间的能量损失。

BSPDN 的主要目标是增加单元的功率,这可以改善许多方面的性能。信号长度减少方面得改进得一个很好的例子。缩短信号长度可以实现更好的路由,并且通过电路发出指令时浪费的能量更少。通过缩短信号长度,提高了能源效率。深度复杂的前端信号网络的问题之一是海豚效应,即当信号在信号层上下移动并产生不必要的复杂性时。BSPDN 解决了这个问题。

BSPDN 另一个有趣的方面是小区略有缩小。单元是印刷到晶圆中的晶体管的标准单元,如果您查看以下数据,PowerVia 的单元高度更小,这意味着更好的设计将使晶体管「缩小」。背面接触将把这个提升到一个全新的水平。

BSPDN 旨在解决这些架构和供电限制。该方法完全解耦供电和信号网络,并使用晶圆的背面来适应配电。使用晶圆的背面,三星和其他半导体制造商可以通过更短、更宽的线路直接供电,从而提供更小的电阻、更高的供电性能并减少路由拥塞。

虽然从 FSPDN 到 BSPDN 的转变听起来很有希望,但仍有一些挑战阻止它成为追求该技术的制造商的标准方法。

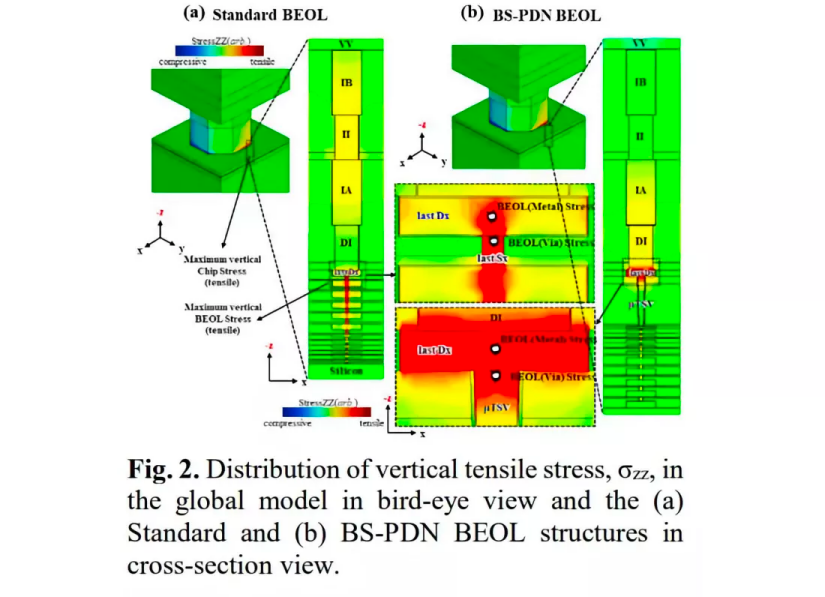

三星在研讨会上提出了实施新电力传输模型的最大挑战之一,即与 BSPDN 相关的拉伸强度可能会降低。应用时,BSPDN 可以减少拉应力作用和硅通孔电极(TSV),导致与金属层分离。

三星表示,这个问题可以通过降低高度或加宽 TSV 来解决,但更多在正式宣布解决方案之前,需要进行研究和测试。要成功应用 BSPDN,还需要在信号和电力线连接方面取得更多进步。除了上述之外,还需要在化学机械抛光 (CMP) 技术方面取得进步。当前的 CMP 实施用于从晶圆背面去除 5 至 10 微米的「峰谷」。实施 BSPDN 可能需要一种新的方法来抛光晶圆而不损坏底层功率元件。

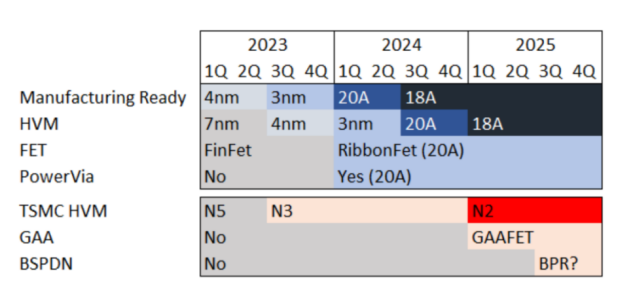

三星目前没有概述基于 BSPDN 的架构的正式实施的时间表,但在背面供电领域,另一家制造巨头也已经开始了布局。在 2023 年 VLSI 研讨会上,英特尔展示了制造和测试其背面供电解决方案 PowerVia 的过程,并取得了良好的性能测试结果。英特尔正在大胆下注,在台积电之前采用 PowerVia,通过使用 RibbonFET(他们对 GAA 的改进) 来做到这一点。台积电插入 BSPDN 最晚可能会在 2026 年发生,与此同时英特尔希望 2024 年推出 PowerVia。

英特尔团队制作了称为 Blue Sky Creek 的测试芯片,该芯片基于英特尔即将推出的 PC 处理器 Meteor Lake 中的能效核——证明 PowerVia 解决了旧方法造成的两个问题。现在电源线和互连线可以分离开来并做得更宽,同时改善供电和信号传输。

对于普通计算机用户来说,这意味着降低能效和提高速度。在降低功耗的情况下更快地完成工作,再次延续摩尔定律的承诺。使用 PowerVia 设计的英特尔能效核实现了 6% 的频率增益和超过 90% 的标准单元利用率,调试时间与 Intel 4 一样,在可接受的范围内。对于仅仅移动电源线来说,这是「巨大」的频率提升。

Intel 20A 将是英特尔首个采用 PowerVia 背面供电技术及 RibbonFET 全环绕栅极晶体管的节点,预计将于 2024 年上半年实现生产准备就绪,应用于未来量产的客户端 ARL 平台,目前正在晶圆厂启动步进(First Stepping)。

评论