FIR结构IQ串行处理RRC滤波器

2.2 串行处理滤波器结构

其后采用FIR结构实现RRC滤波器,其中数据输入端使用IQ路串行输入,即上一节中的串行数据。由于奇数阶M=65FIR滤波器的时域特性,其冲击响应满足如下条件:

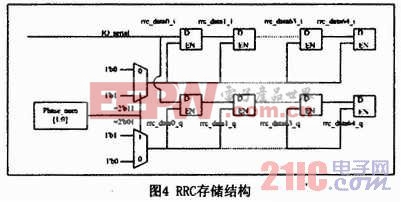

因此对于不同部分的存储单元可以使用相同的加法单元,在下面的复用乘加器中可以设计复用结构。这里描述FIR数据存储的结构,其中由计数器Phase_num控制数据在滤波器存储单元中的流动。高位为1时存储I路数据,高位为0时存储Q路数据。数据存储单元无法复用,因为这是滤波必需的。但是乘加器则可以通过如下小节中描述的方式复用。本文引用地址://www.cghlg.com/article/179110.htm

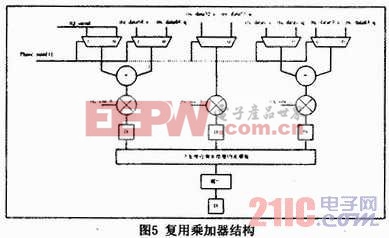

2.3 复用乘加器结构

同样,依靠计数器控制,我们可以复用同一套乘加资源,但是存储单元依然和使用两套FIR结构相同,这也体现了ASIC设计的本质。从图5中我们就可以发现乘加器的输入也由同一个计数器控制,计数器高位为1时,计算I路数据滤波结果,计数器高位为0时,计算Q路滤波结果,随后经过两级触发器缓存,在输出端形成串行IQ路数据,如此结构就节省了两套FIR滤波器中的乘法器与加法器的结构,当FIR阶数较高时就有效地节省了资源,但是这是有前提的,即射频部分在下变频时并没有残留太大的频偏,也就是说当基带信号并不是很理想时,或者有一个带通信号对其进行干扰时,IQ路RRC滤波器是不一样的,那么此时滤波系数就是不同的,则不可避免地需要两套RRC结构。

3 结论

本文通过改变通常FIR处理结构,有效地节省了资源,只使用了一套乘加器,一套FIR滤波器结构,就完成了两套FIR滤波器的功能,虽然数据存储单元与两套FIR相比并未减少,但是有效地减少了乘加资源的使用,提高了运算效率,节省了ASIC芯片的面积。当RRC滤波器阶数

较高时,效果更为明显。

评论